# SOLUTION PROCESSED THIN FILM TRANSISTORS FOR ORGANIC LIGHT EMITTING DIODE BACKPLANE

#### **GUPTA MIHIR**

SCHOOL OF ELECTRICAL AND ELECTRONIC ENGINEERING

A DISSERTATION SUBMITTED IN PARTIAL FULFILMENT OF THE REQUIREMENTS FOR THE DEGREE OF MASTER OF SCIENCE IN MICROELECTRONICS

2015

#### **Abstract**

Solution processed electronics is a low cost device fabrication methodology that has gained research interest over past two decades. The continuous rising of this field is due to the increasing number of discoveries and research work being done alongside in material science domain, providing it new alternatives and techniques to enhance the device performance. The main idea of solution processed electronics is to fabricate a large number of devices that show optimal performance in an inexpensive way, and trying to eliminate certain processes and infrastructures that need a lot of expenditure like high class cleanrooms. A parallel motive to undertake this research is also to develop devices using such materials that can enable us to create a flexible and a transparent device.

These type of devices are the main interest of the research. Focused on understanding and designing new fabrication methodology for Thin Film Transistors (TFT) is the key objective of this research. During the experimentation period of this research project, various materials and device structures were tried and tested to produce an optimized TFT that will be used in the backplane of an OLED and will be used to switch the OLED on and off. Hence the requirements for the output parameters of the TFT were known in the beginning in accordance with the OLED it needs to switch. The transistor parameters like ON current, OFF current, gate leakage, threshold voltage, mobility and ON/OFF ratio were optimized.

The device architecture was also the research focus and two designs were developed, tested and optimized. These different designs were aimed at different type of applications of the OLED, which the TFT will be driving. The first type was the segmented device and the second type was the pixelated device. The basic difference between the two devices is in the size, but in order to fabricate the devices, the process used was a lot different from each other. For the segmented device, conventional thin film deposition techniques were used like spin coating and physical vapor deposition. For the pixelated device in addition to the conventional techniques, some additional processes were also used like photolithography, making it more complex compared to the segmented device.

## Acknowledgements

I would like to thank my thesis supervisor Prof Dr Subodh Gautam Mhaisalkar for providing me this amazing opportunity to work at the Energy Research Institute @ NTU (ERI@N) and for his guidance throughout the project. I am very grateful to my mentor Dr Zhang Keke for the inspiring discussions and the invaluable advice he provided in order to keep my work on track and also for my future career. His mentoring from the very start of the project and training me on various equipment were very essential ingredients for me to complete this thesis timely and successfully. I am fortunate to be mentored by him, and would like to thank him very much for all his help. I would also like to thank my colleague Rohit John Abraham, who guided me for the experiments and my coursework as well. In addition I really appreciate all the help, discussions and suggestion I was given by Mr Sudhandhu Shukla, Mr Rajiv Ramanujam and my other lab mates and co-workers here at ERI@N.

I would also like to take this opportunity to thank my batch mates Skand Kumar Sharma, Chaitanya Nair, Shashank Juyal and Nakul Narang for their support and encouragement throughout the master degree coursework.

Finally I would like to thank my parents and my brother for their endless encouragement and love, and for offering me an opportunity to pursue my dreams.

Gupta Mihir January 2015

"I just try to have fun, it's about having a good time."

— Lemmy Kilmister

## Table of Contents

| Abstrac   | t                                                           | i    |

|-----------|-------------------------------------------------------------|------|

| Acknow    | vledgements                                                 | ii   |

| List of I | Figures                                                     | viii |

| List of T | Γables                                                      | xii  |

| Acrony    | ms                                                          | xiii |

| Disserta  | ation Outline                                               | xiv  |

| Chapter   | 1: Introduction                                             | 1    |

| 1.1       | Microelectronics and Macroelectronics                       | 2    |

| 1.2       | Current State with Solution Based Electronics               | 2    |

| 1.3       | Solution process based materials                            | 4    |

| 1.4       | Inorganic and Organic Materials                             | 4    |

| 1.5       | Solution Processed Transparent Conductive Oxides            | 5    |

| 1.5       | .1 Nanoparticles                                            | 5    |

| 1.5       | .2 Nanowires                                                | 5    |

| 1.5       | .3 Solution Deposited Thin Film                             | 6    |

| 1.6       | Carrier Transport in Amorphous Metal Oxides                 | 6    |

| Chapter   | 2: Literature Survey                                        | 10   |

| Chapter   | 3: Field Effect Transistor Theory                           | 17   |

| 3.1       | The Metal-Oxide-Semiconductor (MOS) Capacitor and Operation | 18   |

| 3.1       | .1 Accumulation Case                                        | 21   |

| 3.1       | .2 Depletion Case                                           | 22   |

| 3.1       | .3 Inversion Case                                           | 22   |

| 3.2       | MOSFET Operation                                            | 25   |

| 3.3       | MOSFET Characteristics                                      | 26   |

| 3.3       | .1 Output Characteristics                                   | 26   |

|   | 3.3.   | .2 Transfer Characteristics                                  | 28 |

|---|--------|--------------------------------------------------------------|----|

|   | 3.4    | Comparison of a MOSFET and a Thin Film Transistor (TFT)      | 31 |

| С | hapter | 4: Experimental Procedure                                    | 33 |

|   | 4.1    | Substrate Preparation                                        | 34 |

|   | 4.2    | Semiconductor Precursor Synthesis (ZTO)                      | 35 |

|   | 4.3    | Segmented TFT Device Fabrication Process                     | 36 |

|   | 4.3.   | .1 ZTO Spin coating                                          | 36 |

|   | 4.3.   | .2 Source and Drain Electrode Deposition                     | 37 |

|   | 4.3.   | .3 Dielectric Synthesis and Spin coating                     | 38 |

|   | 4.3.   | .4 Gate Electrode Deposition                                 | 39 |

|   | 4.4    | Pixelated TFT Device Fabrication Process                     | 40 |

|   | 4.4.   | .1 ZTO Spin Coat                                             | 40 |

|   | 4.4.   | .2 Photolithography for Source and Drain Electrode Formation | 41 |

|   | 4.4.   | .2 Source Drain Electrode Deposition                         | 43 |

|   | 4.4.   | .3 Source and Drain Photoresist Removal                      | 43 |

|   | 4.4.   | .4 Dielectric Synthesis and Spin Coat                        | 44 |

|   | 4.4.   | .5 Photolithography for Gate Electrode Formation             | 45 |

|   | 4.4.   | .6 Gate Electrode Deposition                                 | 46 |

|   | 4.4.   | .7 Gate Photoresist Removal                                  | 46 |

| С | hapter | 5: Results and Analysis                                      | 48 |

|   | 5. 1   | Segmented Device                                             | 48 |

|   | 5.1.   | .1 Effect of Change in Ionic Concentration                   | 48 |

|   | 5.1.   | .2 Effect of Dielectric Spin Time                            | 49 |

|   | 5.1.   | .3 Final Optimized Device                                    | 51 |

|   | 5.1.   | .4 OLED Switching Using the Segmented Device                 | 53 |

|   | 5.1.   | .5 Segmented Thin Film Transistor Statistics                 | 55 |

| 5.2 Pi     | xelated Device                                | 57 |

|------------|-----------------------------------------------|----|

| 5.2.1      | Effect of Ionic Concentration                 | 57 |

| 5.2.2      | Effect of Dielectric Spin Speed               | 60 |

| 5.2.3      | Effect of Additive PMF to the Gate Dielectric | 63 |

| 5.2.4      | Final Optimized Pixelated Device              | 65 |

| Chapter 6: | Conclusion and Future Work                    | 67 |

| Appendix   |                                               | 70 |

| MATLA      | B Codes for Statistics Calculations           | 70 |

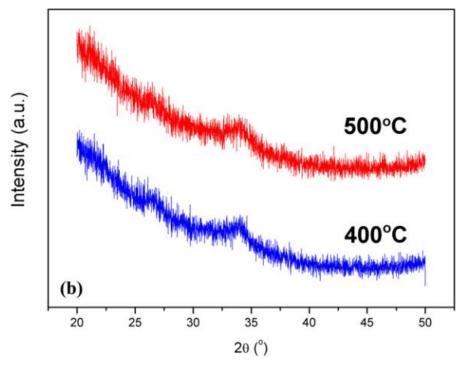

| XRD for    | Zinc Tin Oxide (ZTO)                          | 71 |

| List of To | ools Used                                     | 71 |

| References |                                               | 72 |

"The first principle is that you must not fool yourself and you are the easiest person to fool."

— Prof Richard Feynman

## **List of Figures**

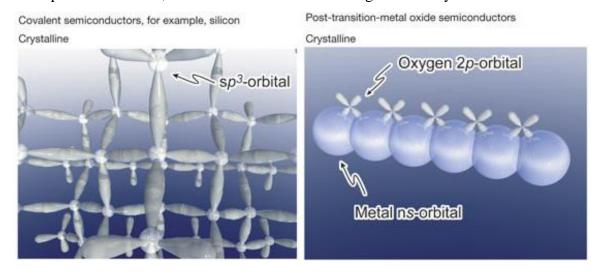

| Figure 1: In case of crystalline semiconductors, the overlapping (if covalent) takes   |

|----------------------------------------------------------------------------------------|

| place among highly directional sp3 orbitals, and (if with metal ion) takes             |

| place between metal ns orbitals which are isotropic. From the figure we can            |

| see that the oxygen 2p overlapping is negligible [11]8                                 |

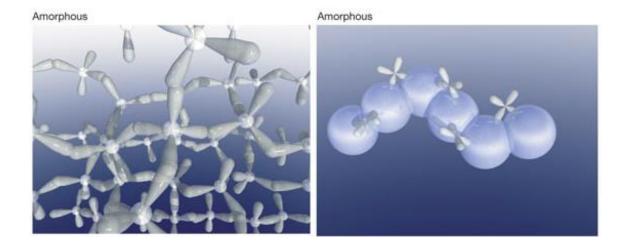

| Figure 2: In case of amorphous semiconductors, when overlapping occurs between         |

| highly directional sp3 orbitals, there is a huge randomness in overlapping             |

| and hence the carrier transportation is inefficient; while in case of                  |

| amorphous oxide semiconductors with metal cations, the randomness does                 |

| not affect this overlapping of ns metal orbitals because of their isotropic            |

| nature [11]8                                                                           |

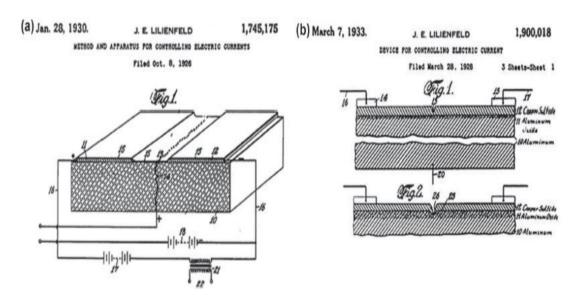

| Figure 3: Patent structures by Lilienfeld- MESFET (left) and MISFET (right) 10         |

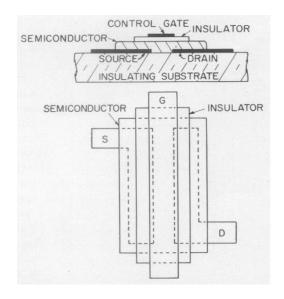

| Figure 4: Cross section and also the plan view of an evaporated thin film transiston   |

| [18, 19]11                                                                             |

| Figure 5: 1 inch square glass slide (attached on a lucite slab)with 3 TFT's fabricated |

| on it [18, 19]11                                                                       |

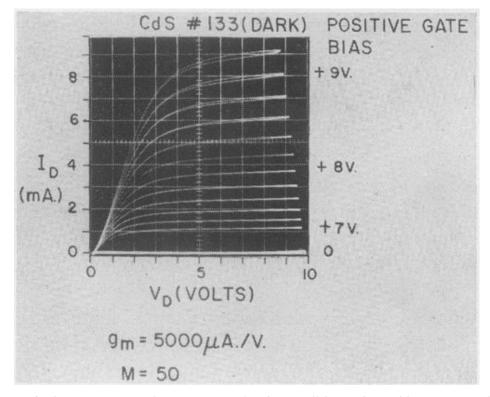

| Figure 6: Characteristic curves for an experimental Cadmium Sulfide TFT designed       |

| for operation in the "enrichment" mode (Enhancement Mode) [18, 19] 11                  |

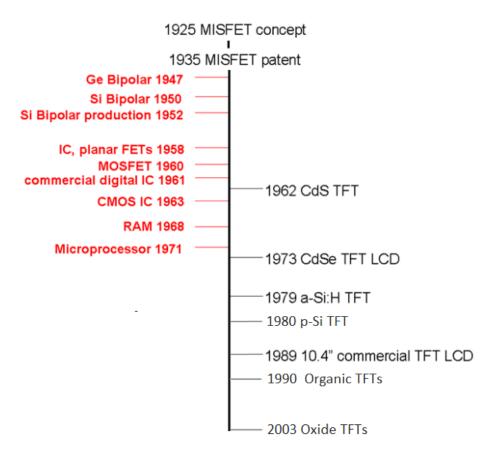

| Figure 7: Timeline for Thin Film Transistors along with landmarks in IC                |

| development [37]14                                                                     |

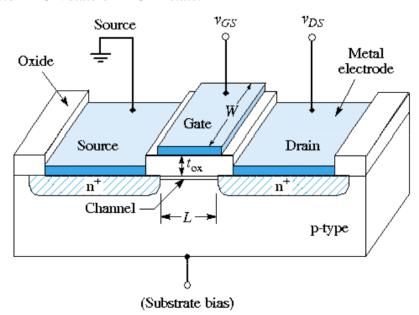

| Figure 8: Schematic diagram of an n-cannel enhancement mode MOSFET [38] 17             |

| Figure 9: Basic MOS structure                                                          |

| Figure 10: MOS band diagram before contact                                             |

| Figure 11: Energy Band Diagram for an ideal Metal Oxide Semiconductor structure        |

| at equilibrium [39]19                                                                  |

| Figure 12: Band Diagram for MOS structure after contact                                |

| Figure 13: Accumulation Case in p-type                                                 |

| Figure 14: Depletion Case in p-type                                                    |

| Figure 15: Inversion Case in p-type                                                    |

| Figure 16: Analytical relation for surface and bulk potentials                         |

| Figure 17: The surface charge density Qs compared for both p-type and n-type           |

|----------------------------------------------------------------------------------------|

| semiconductors depending on. $\psi_{s.}$ While the solid lines stand for positive      |

| Qs, the dashed lines symbolize negative Qs. [40]                                       |

| Figure 18: Cross section view of an n-channel MOSFET, showing the field oxide and      |

| polysilicon gate [38]25                                                                |

| Figure 19: Channel formation in an NMOS with the application of gate voltage and       |

| drain voltage [39]                                                                     |

| Figure 20: NMOS output characteristics for linear/ triode region                       |

| Figure 21: NMOS output characteristics for saturation region                           |

| Figure 22: NMOS in saturation region showing Pinch-off region                          |

| Figure 23: Transfer Characteristics of a 32 nm Intel PMOS and NMOS showing ~           |

| 100mV/decade slope at V <sub>DS</sub> =1.0V and 50mV [41]                              |

| Figure 24: MOSFET (left) and TFT (right)                                               |

| Figure 25: Different types of TFT structures [42]                                      |

| Figure 26: Final TFT device schematic                                                  |

| Figure 27: Effect of S/D electrode thickness on dielectric layer deposition 37         |

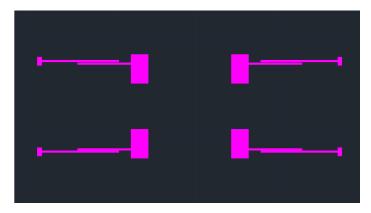

| Figure 28: Source and drain mask with contact pads for terminal ends                   |

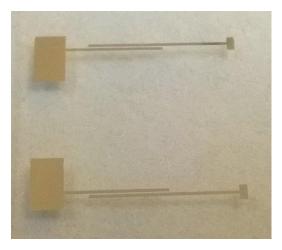

| Figure 29: Metallized source and drain terminals with channel gap between them         |

| below them is a ZTO layer                                                              |

| Figure 30: Gate mask with contact pad at the terminal end                              |

| Figure 31: Gate mask overlapped with the source and the drain mask                     |

| Figure 32: ZTO spin coated on Quartz wafer (some dust particles can be seen on the     |

| coating)40                                                                             |

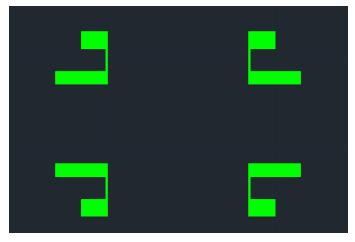

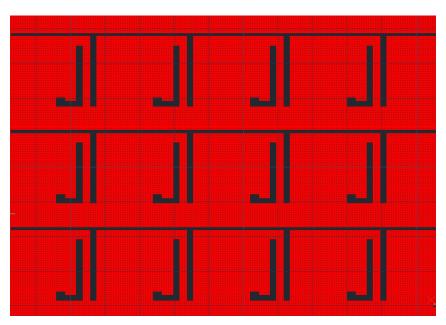

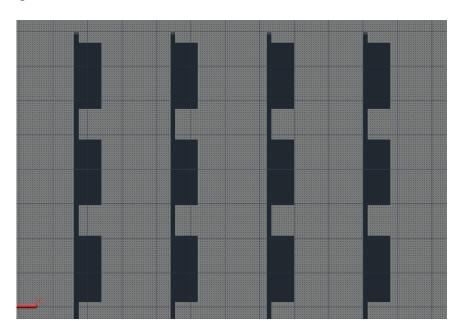

| Figure 33: Photolithography mask for source and drain terminals with devices           |

| connected in series                                                                    |

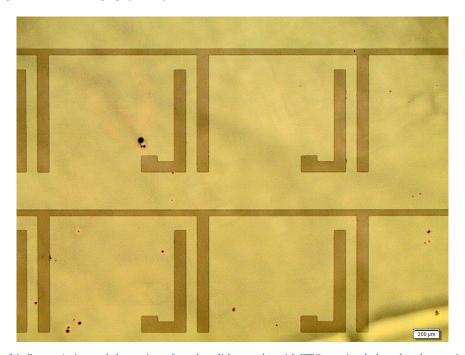

| Figure 34: Source/rain mask formation after photolithography with ZTO coating          |

| below the photoresist layer (The design is the portion where there is no               |

| photoresist)                                                                           |

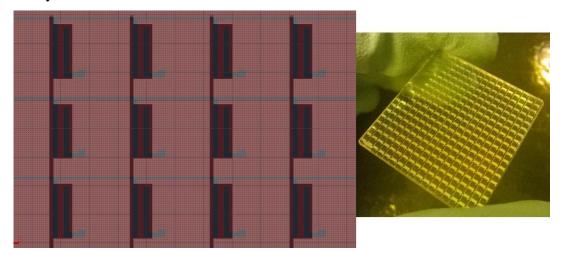

| Figure 35: Photolithography mask for Gate formation connected in series                |

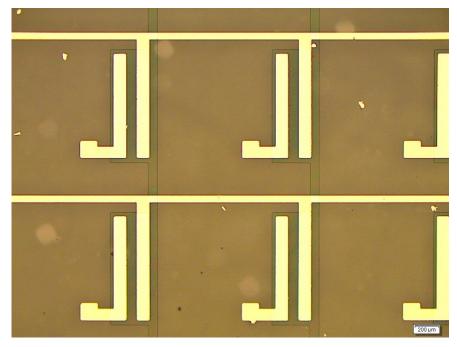

| Figure 36: Metallized source/drain electrodes can be seen, with transparent dielectric |

| above it, and then the gate mask formation after the photolithography                  |

| process                                                                                |

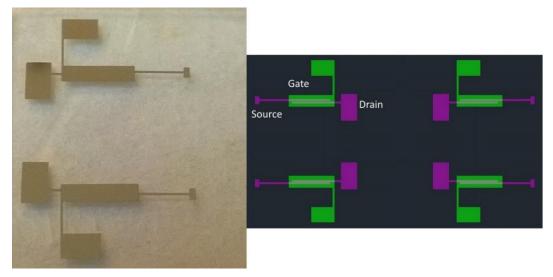

| Figure 37: Overlap of Source/Drain and Gate masks                                                           |

|-------------------------------------------------------------------------------------------------------------|

| Figure 38: Final pixelated device with gate metallization above source and drain. The                       |

| vertical metal strip connects all the drain electrodes and the horizontal strip                             |

| connects all the gate electrodes                                                                            |

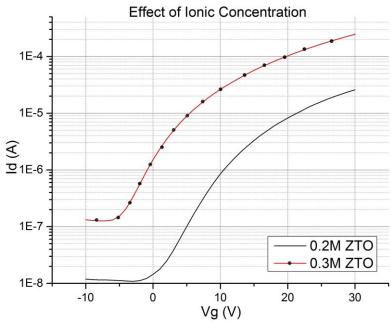

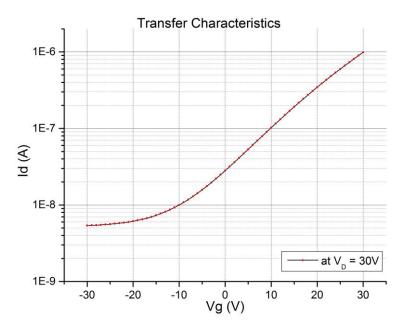

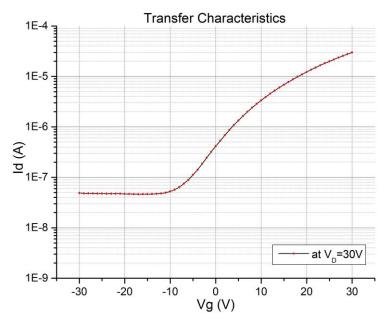

| Figure 39: Transfer Characteristics (I <sub>D</sub> -V <sub>G</sub> ) for 0.2M and 0.3M ionic concentration |

| ZTO Segmented TFT                                                                                           |

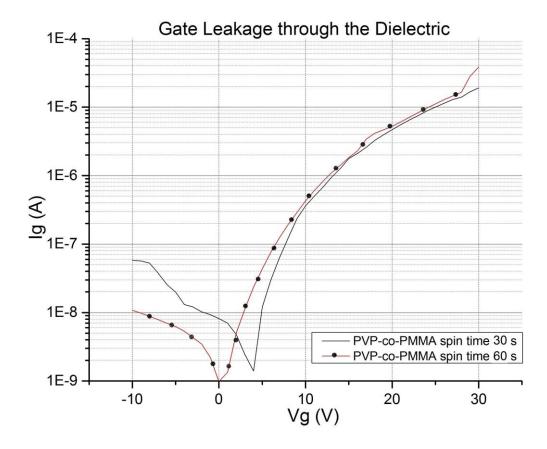

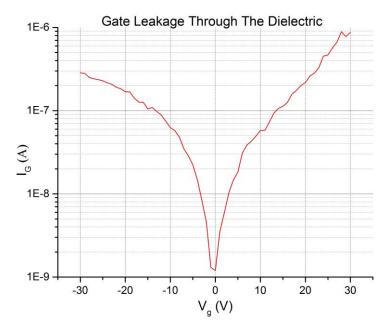

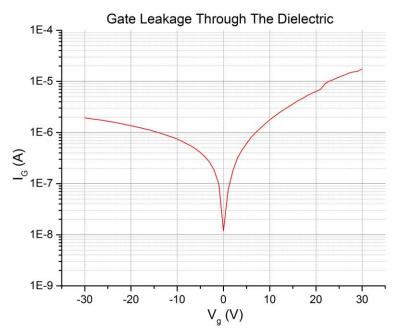

| Figure 40: Gate Leakage through the dielectric with variation in dielectric spin time                       |

| 49                                                                                                          |

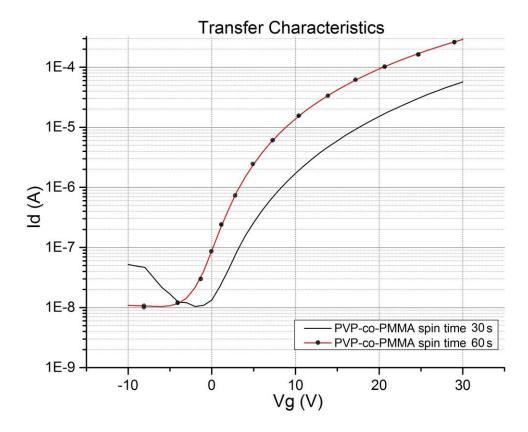

| Figure 41: Transfer Characteristics (I <sub>D</sub> -V <sub>G</sub> ) for 0.2M ionic concentration ZTC      |

| Segmented TFT with varying dielectric spin time                                                             |

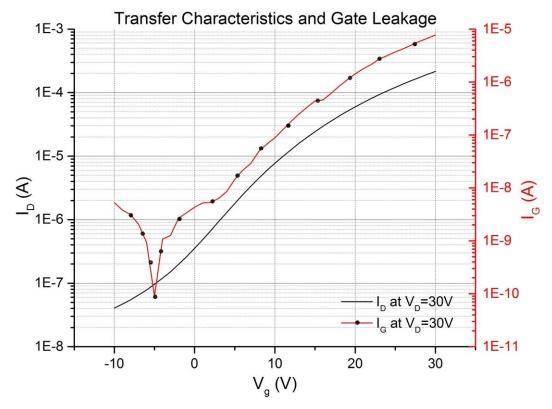

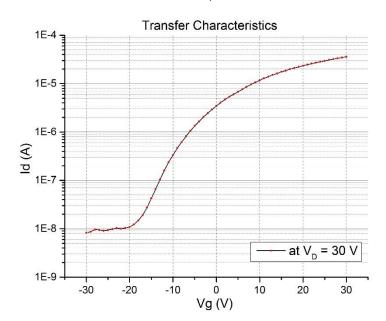

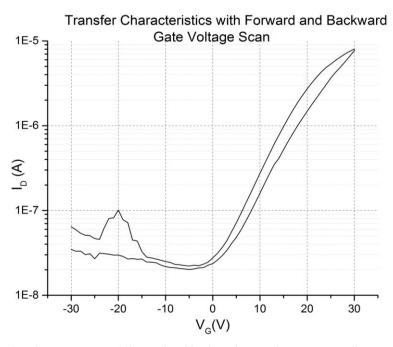

| Figure 42: Final Device Transfer Characteristics (left black axis) with Gate leakage                        |

| (right red axis)                                                                                            |

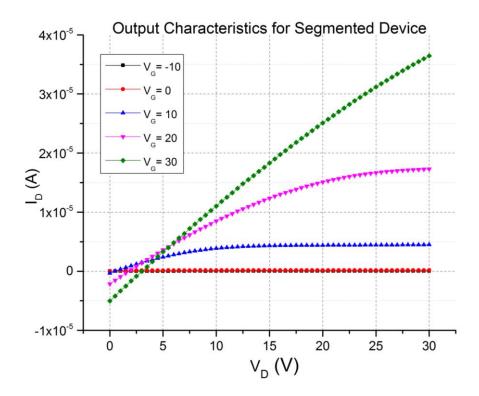

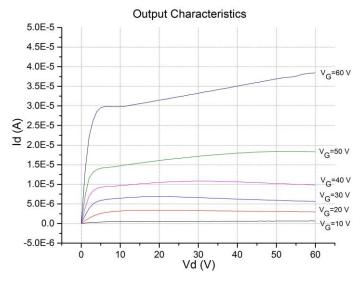

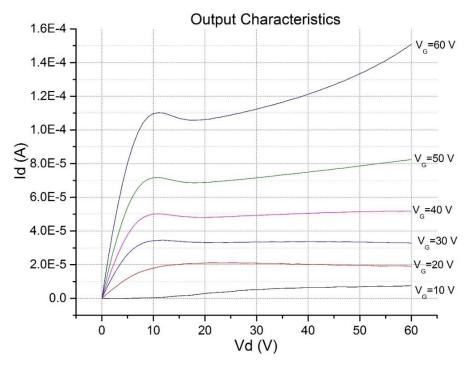

| Figure 43: Output Characteristics for Segmented Device                                                      |

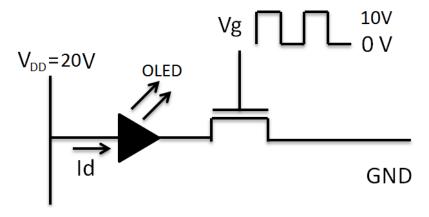

| Figure 44: The OLED switching circuit diagram                                                               |

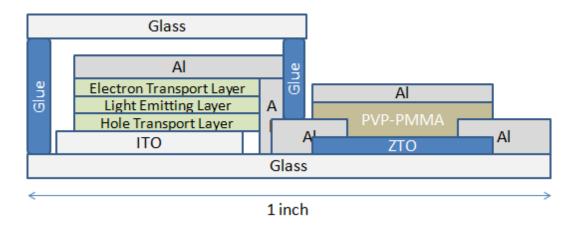

| Figure 45: TFT device and the OLED structure schematic                                                      |

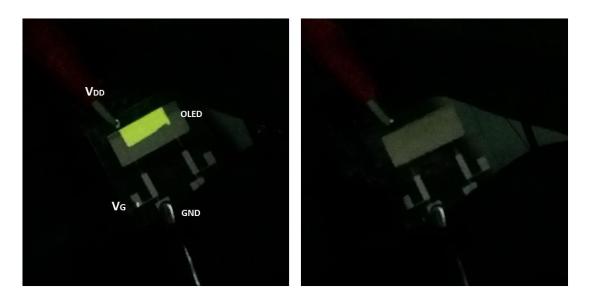

| Figure 46: OLED switched ON (left) and switched OFF (right)                                                 |

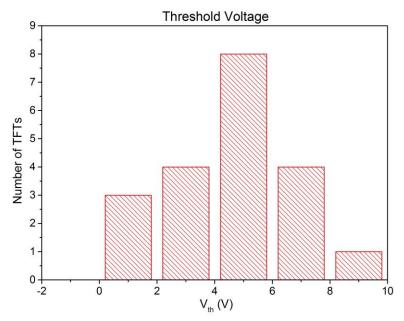

| Figure 47: Threshold voltage distribution                                                                   |

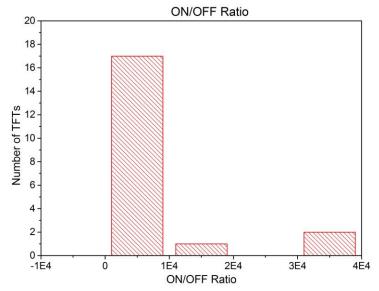

| Figure 48: ON/OFF Ratio distribution                                                                        |

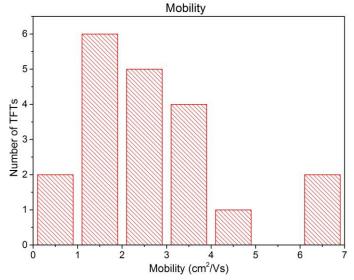

| Figure 49: Mobility distribution                                                                            |

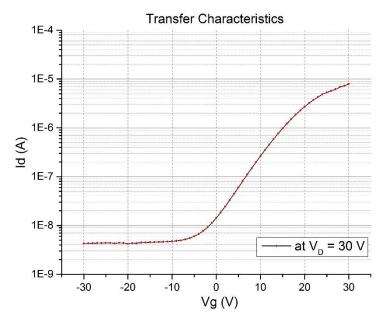

| Figure 50: Transfer Characteristics ( $I_D$ - $V_G$ ) for 0.3M ionic concentration ZTC                      |

| Pixelated TFT with W/L as 890/100 μm58                                                                      |

| Figure 51: Transfer Characteristics ( $I_D$ - $V_G$ ) for 0.4M ionic concentration ZTC                      |

| Pixelated TFT with W/L as 890/100 μm58                                                                      |

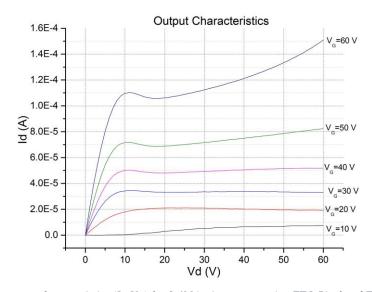

| Figure 52: The output characteristics $(I_D - V_D)$ for 0.3M ionic concentration ZTC                        |

| Pixelated TFT with W/L as 890/100 μm59                                                                      |

| Figure 53: The output characteristics $(I_D - V_D)$ for 0.4M ionic concentration ZTC                        |

| Pixelated TFT with W/L as 890/100 μm59                                                                      |

| Figure 54: Gate dielectric leakage plot for PVP-co-PMMA + PMF dielectric spir                               |

| coated at 1000 rpm for 60 seconds; gate leakage of $1\mu A$ at $V_G = 30V61$                                |

| Figure 55: Gate dielectric leakage plot for PVP-co-PMMA + PMF dielectric spir                               |

| coated at 2000 rpm for 60 seconds; gate leakage of 10.8 µA at V <sub>G</sub> =30V 61                        |

| Figure 56: Transfer characteristics for PVP-co-PMMA + PMF dielectric spin coated     |

|--------------------------------------------------------------------------------------|

| TFT at 1000 rpm for 60 seconds; ON current of $1\mu A$ at $V_G=30V$                  |

| Figure 57: Transfer characteristics for PVP-co-PMMA +PMF dielectric spin coated      |

| TFT at 1000 rpm for 60 seconds; ON current of $12\mu A$ at $V_G$ =30V                |

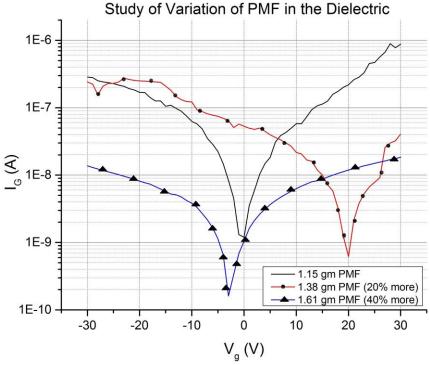

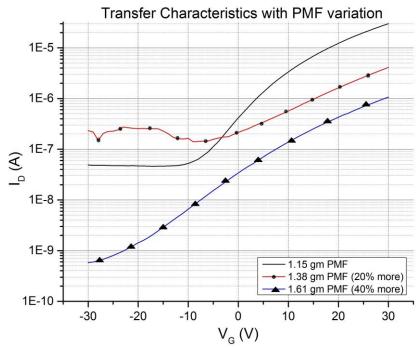

| Figure 58: Study of variation of PMF percentage in the dielectric                    |

| Figure 59: Transfer Characteristics for TFTs with variation on PMF percentage in the |

| dialoguia                                                                            |

| dielectric                                                                           |

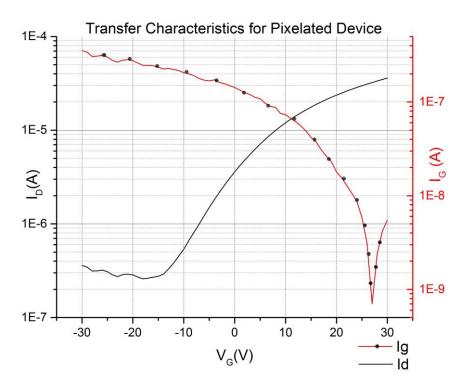

| Figure 60: Final Transfer Characteristics of Pixelated Device                        |

|                                                                                      |

| Figure 60: Final Transfer Characteristics of Pixelated Device                        |

| Figure 60: Final Transfer Characteristics of Pixelated Device                        |

## **List of Tables**

| Table 1: Applications of TFTs [37]                                            | 15 |

|-------------------------------------------------------------------------------|----|

| Table 2: ZTO recipes for different ionic molar concentrations                 | 35 |

| Table 3: Film thickness [μm] of photoresist AZ5214E as function of spin speed | 41 |

## **Acronyms**

AOS Amorphous Oxide Semiconductors

a-Si:H Amorphous – Silicon : Hydrogen

OLED Organic Light Emitting Diode

TFT Thin Film Transistor

FET Field Effect Transistor

ZTO Zinc Tin Oxide

IZTO Indium Zinc Tin Oxide

ITO Indium Tin OxideUV Ultra Violet rays

PEDOT:PSS Poly(3,4-ethylenedioxythiophene) Polystyrene Sulfonate

MBE Molecular Beam Epitaxy

PLD Pulsed Laser Deposition

CVD Chemical Vapour Depositi

CVD Chemical Vapour Deposition

PET Polyethylene terephthalate

PEN Polyethylene 2,6-naphthalate

JFET Junction Field Effect Transistor

MESFET Metal Semiconductor Field Effect Transistor

SiO<sub>2</sub> Silicon Dioxide

E<sub>i</sub> Intrinsic Fermi Level

E<sub>f</sub> Fermi Level

CBM Conduction Band Minimum

VBM Valance Band Maximum

TCO Transparent Conductive Oxide

PVP Poly(4-vinylphenol)

PMMA Poly(methyl methacrylate)

PMF poly(melamine-co-formaldehyde)

PGMEA Propylene Glycol Methyl Ether Acetate

### **Dissertation Outline**

The object of this dissertation is to investigate two different Thin Film Transistor designs on transparent substrate, develop low cost fabrication process and optimize them to meet the specifications as to drive and switch OLEDs.

The thesis is divided into 6 chapters. **Chapter 1** is the introductory chapter giving a brief account of the background, current work and the experiments done in this thesis. It also includes the theoretical and practical understanding width wise in the fields associated with Thin Film Transistors and materials. **Chapter 2** deals with the literature survey, and includes all the work being done in the past till today in the field of TFT and conductive oxides. **Chapter 3** explains the theory behind the working and the operation of field effect devices like MOSFET and TFT, and explains the analysis of I-V characteristics. The **chapter 4** includes the work done in this thesis and the experimental part for both the TFT designs. Thereafter the **chapter 5** is the most important chapter and explains the result and the analysis portion of the experiments done. Finally **chapter 6** concludes the results and gives a short account of the possibilities of the future work that can be carried out.

## **Chapter 1: Introduction**

Solution based and printed electronics is a unique branch in Nanoelectronics that complements the conventional Silicon based technology, facilitating low cost solutions to electronic devices and circuits on transparent and/or flexible substrates. This field is continuously revolutionizing and improvising to provide everyday need based 'smart' solutions that are being seen everywhere. Ranging from highly complicated medical sensors and devices to ubiquitous entertainment gadgets and displays, printed and solution based electronics has a large application area. Displays that can be folded like paper, medicines injected in the body through painless patches, solar cells, various kinds of sensors to detect gases, food spoilage, leakage etc. are some of the most popular applications of printed electronics.

All these application can be successfully implemented if the industry can profitably mass produce backplane driver and switching circuits to make these sensors and displays work effectively. These backplane circuits must have the same physical characteristics as that of the device so as to facilitate best usage and compatibility. For example, backplane driver circuit for a skin compatible flexible gadget must also be flexible and transparent for successful integration with the device. Hence here we have the main challenge to overcome these barriers.

The backplane is made up of Thin Film Transistors (TFTs) that switches and drives the device. These TFTs can be manufactured by various methods and various materials can be used depending upon the physical and electrical characteristics of the device it will drive and switch. Most popular methods include solution based processing, inkjet printing and screen printing.

For applications like displays and OLEDS, we need transparent TFT panel as driver circuitry. Transparent conductive oxides have received much attention in the recent years for their suitable properties to be used for displays and flexible electronics. Transparent conductors like Indium Tin Oxide (ITO) has been commercially in use for quite some time now [1]. A lot of research is being done on Zinc Oxide and Indium Tin Oxide. These materials can be used for large area electronics and have huge potential also because they are cheap. An effort is also being made to reduce

the cost of the processing as well. Hence the processes like screen printing and inkjet printing that can reduce the cost by elimination the need of photolithography and expensive cleanrooms.

#### 1.1 Microelectronics and Macroelectronics

Microelectronics as the word suggests includes the study of devices and circuits in micron range or below. It is mainly developed using Silicon as semiconductor and its focus is on developing cheap, high efficiency and high yield devices that can be used for applications like computing, communication devices, memory storage etc. Hence more and more stress is laid on making the device work faster at low operating voltage and at cheaper price. The state-of-the are devices in this domain have gate length of 14 nm, and they are currently in high volume manufacturing by Intel [2].

Macroelectronics on the other hand although lays stress on the performance and yield too, but the real focus for it is to make devices as cheap as possible, for applications that do not need high sophisticated circuitry. These applications include display technology, use and throw electronics including detectors/sensors, biomedical devices that are required to be discarded after single use and similar devices. It is proposed that the fabrication of such devices can further be made cheaper if they will not involve conventional Silicon manufacturing techniques like lithography, reactive ion etching, high temperature annealing etc. Eliminating these processes will eliminate the need for a high class cleanroom and the expenditure associated with it. Hence it is important to make these devices very cheap so they can fall under affordable limit, with a trade-off with the performance, technology and efficiency.

Another advantage macroelectronics seeks as compared to microelectronics is its ability that it can fabricate transparent devices and also flexible ones, which is not possible to achieve with conventional Silicon technology. Hence these are the possible areas that are needed to be explored in macroelectronics.

#### 1.2 Current State with Solution Based Electronics

Solution based electronics unlike conventional Silicon based electronics makes use of bottoms up approach to fabricate devices. Conventional Silicon fabrication

methodology makes use of top-bottom approach in which the Silicon substrate is used as a base, and lithography and etching is performed to get the desired structure. The Silicon substrate is first coated with a photoresist by spin coating. Then the top part of the wafer which is coated with photoresist is covered with a mask and exposed to Ultraviolet light (UV) of specific wavelength to modify the exposed portion of the mask. Subsequently the wafer is then selectively etched or dipped in a developer solution to remove the unwanted portion of the masked wafer in order to obtain a pattern. This pattern is then used as a mask in itself for further processing. This is a generalized process for Photolithography to obtain a pattern and involves a lot of steps depending on the pattern and the material used. On the contrary, then we talk about printed electronics, we need just on single step and that would be direct printing of the pattern on the substrate. If it is screen printing, then the substrate is places below a mesh (that hold a pattern), and the ink or the paste is patterned on the substrate directly via the small holes in the mesh. If it is ink jet printing, then the substrate is kept on the ink jet printer's paten and a jet nozzle continuously drops ink to create the desired pattern. This pattern can then be forwarded for subsequent annealing and processing. Hence the overall process is simpler when compared with conventional fabrication and processing.

As we can see that solution based electronics is a much faster way to make electronics circuits and one can directly make patterns without the need to involve multiple steps. This is of a great advantage when we are concerned with macro electronics as opposed to microelectronics. For macroelectronics, the main issue is cost-effectiveness whereas for microelectronics although cost is an issue but the industry is also much concerned about the performance and the yield of the process. Hence even if there is degradation in performance as compared to conventional devices, they can still be used for the display, driver circuit and similar applications, but the important criterion is that they must be manufactured cheap.

Although there are some compromises that are needed to be considered when using solution based electronics. The main issues are with the device performance and device construction and substrate preparation (surface adhesiveness). The device performance including parameters like mobility, On-Off ratio and Threshold Voltage are not up to the mark as achieved with conventional technology. The main reason

for this is suspected to be the non-uniformity in the solution deposition while printing, the issues associated with the surface adhesiveness, residual solution and gas trapping while annealing. These variables influence the performance of the devices varying their parameters with each batch. For the device construction issue, the minimum feature size is a constraint. The line width obtained by photolithography is substantially less than obtained with printing. This limits the application areas for the device and hence increasing the cost of production.

#### 1.3 Solution process based materials

As mentioned earlier there has been substantial amount of research going on for materials that are compatible with solution processing. Semiconductor inks like Zinc Oxide (ZO), Indium Zinc Tin Oxide (IZTO) etc. have been researched extensively and good reports have been published on improved transistor parameters like mobility and On-Off ratio. Printing is not only done for the semiconductor but also for conductors and for making electrical components. Carbon is very well known to be screen printed and used both as electrode as well as a resistor [3]. Other materials like metal nanoparticles (Au, Ag, and Cu) can be inkjet printed to form conductive paths. Hence in this way we can make use of these materials to form a transistor that is totally based on solution based processing. Moreover, a good amount of research is also going to make transparent circuits. Materials like IZTO and ZO are known to be transparent semiconductors which are a very good choice for such circuits. For electrodes and conductive paths there have been reports on using materials like PEDOT:PSS and ITO by inkjet printing [4]. Another alternative is nanoparticles that offer better conductive paths and can be inkjet printed.

The above mentioned semiconductor inks are mostly inorganic materials. There also have been a great deal of research on organic semiconductors, but due to their instability in air and relatively poor mobility, they suffer a lag compared to inorganic semiconductors.

#### 1.4 Inorganic and Organic Materials

As of today we can already see devices made of organic materials like cell phone displays and television displays. They are made of Organic Light Emitting Diodes (OLEDs) which are available as a commercialised device. Hence a lot of research

has already been conducted on organic materials and they have been understood well as compared to inorganic materials. Despite some disadvantages like low mobility, organic materials are easy to print and the annealing temperature needed is low, which reduces the cost of production. When comparing inorganic materials with organic, one can see that inorganic oxides have higher mobility and are stable in air, which is a big advantage. Also not much research has been done on inorganic oxide materials to be used as conductors or semiconductors. Hence there is a wide scope of possibilities in case of inorganic oxides.

Usually we find that the inorganic oxides are n-type semiconductors like Zinc Oxide (ZO), Zinc Tin Oxide (ZTO), Indium Zinc Oxide (IZO) etc. where as in case of organic materials, they usually are p-type semiconductors due to strong trapping of electrons but not holes [5].

#### 1.5 Solution Processed Transparent Conductive Oxides

The solution processing of conductive oxides can be done in the following three ways:

- Nanoparticles

- Nanowires

- Solution deposited thin film

#### 1.5.1 Nanoparticles

This methodology involves suspension of nanoparticles in a solution and then either spin coating the solution or using inkjet printer to make the pattern. Since the surface area to volume ratio of the nanoparticles is more than that of bulk material, we need lower temperature to anneal the thin film. This is a big advantage since low temperature processing reduces the cost of production and also enables processing on substrates that are flexible and transparent like PET and PEN. On heating the deposited pattern, the nanoparticles fuse together to form a crystalline layer.

#### 1.5.2 Nanowires

The process involved in solution processing of the nanowires is somewhat similar to those involving nanoparticles. Though the case with nanowires should theoretically give better performance as they have better transport characteristics, but due to less control on the packing density of the wires, the practical result do not match the theoretical speculations.

#### 1.5.3 Solution Deposited Thin Film

This process involves formation of the conductive oxide not externally but directly on the substrate. This is much different from nanoparticle and nanowire deposition in the way that nanoparticles and wire are already processed before their deposition, but in this case the reaction takes place on the substrate directly. This process has its own pros and cons. A good thing about this process is that the quality and uniformity obtained is much higher than nanoparticles or wires. Although as for the reaction to take place, most of the reactions for the formation of conductive oxides need high temperatures (300 - 600 °C), hence making the process unfavourable for flexible substrate that have low melting point, and also increasing the cost of production. This process can be carried out in the following major forms:

- 1. Spin coating [6]

- 2. Dip Coating [7]

- 3. Sol Gel [8]

- 4. Spray Pyrolysis [9]

The experiments I performed for my thesis work were done using spin coating to fabricate Thin Film Transistors (TFTs) and Zinc Tin Oxide (ZTO) as transparent conductive oxide for semiconductor thin film.

#### 1.6 Carrier Transport in Amorphous Metal Oxides

Amorphous Semiconductors have low mobility when compared with polycrystalline materials. But amorphous materials still have some characteristics that makes them still a viable candidate for certain types of transistors, where mobility is not a concern. These properties include uniformity of device characteristics and low temperature processing [10] [11]. These properties make them useful for our purpose which is for OLED backplane, flexible electronics and also use-and-throw electronic sensors.

Like all the solids, band structures are a good source of information for understanding the electronic properties of metal oxides. But due to complex interaction of the metal orbitals with Oxygen orbitals, the electronic structure of the metal oxides gets complicated. Also there increases a difference in the conduction properties of electrons and holes for these materials. The band gap in case of Silicon if the energy difference between the  $\sigma^*$  -  $\sigma$  levels. These are special hybrid orbitals in conduction band minima and valance band maxima corresponding the antibonding and bonding states in case of Silicon [11, 12]. Due to this the electronic structure of the metal oxides is different from that of a covalent banded semiconductor. In case of the common conductive metal oxides the conduction band and the valance bands are formed by the ns orbital of the metal and the 2p orbital of the oxygen [13]. Due to this the conduction band minima thus formed is highly spread while the valance band maxima is localized. This further leads to the difference in the electron and the hole effective masses, making electrons lighter therefore associated higher mobility for n-type devices. It is one of the main reasons why there are more n-type devices as compared to p-type devices.

The low mobility in amorphous semiconductors can be explained when we study the charge carrier mechanism in the material which is done by "Hoping" mechanism that occurs between localized tail-states, which is different from band conduction [14]. The stated low mobility is linked with the intrinsic feature of the chemical bonds. The carrier transport part in semiconductors that feature covalent bonds like a-Si:H use the sp3 orbitals, which are highly directional. Hence if there is any alteration in the bond angle of these sp3 bonds, this changes the electronic states, which leads to high-density deep tail-states.

Although, there are some amorphous semiconductors that have better performance and higher mobility, like Amorphous Oxide Semiconductors (AOS) that have post-transition metal cations attached to Oxygen molecules forming an M-O-M bond structure. The bottom of the conduction band of the AOS with cation electronic configuration  $(n-1)d^{10}$  ns<sup>0</sup> (with  $n\geq 4$ ) is mainly composed of spatially spread metal ns orbital, and because of the uniform spread of the metal ns orbitals, it allows direct overlap among neighbouring orbitals. This property is very useful as the overlapping is not affected by the amorphous nature of the oxide, and the direct overlapping of the metal orbital is large compared to the 2p overlapping of the Oxygen orbitals (Figure 2)[11].

Therefore, in amorphous oxides (without metal cations), the overlapping occurs only between the directional sp3 orbitals, where as in AOS with metal cations, the amorphous nature does not affect the overlapping as the overlapping is between isotropic metal orbitals, hence in this case we obtain higher mobility.

Figure 1: In case of crystalline semiconductors, the overlapping (if covalent) takes place among highly directional sp3 orbitals, and (if with metal ion) takes place between metal ns orbitals which are isotropic. From the figure we can see that the oxygen 2p overlapping is negligible [11]

Figure 2: In case of amorphous semiconductors, when overlapping occurs between highly directional sp3 orbitals, there is a huge randomness in overlapping and hence the carrier transportation is inefficient; while in case of amorphous oxide semiconductors with metal cations, the randomness does not affect this overlapping of ns metal orbitals because of their isotropic nature [11]

As discussed earlier, that metal oxides have a complicated electronic structure which makes them semiconductor in nature, but their conductivity is comparatively less mainly because of the wide band gap for the materials, due to which there are negligible thermal excitations, hence low intrinsic carrier density. So in order to increase the conductivity, other methodologies are adopted like growing n-type materials in oxygen rich environment. This will increase their conductivity making them more metallic in nature. This finding is based on the experiments that found that electrical conductivity of such materials is associated with non-stoichiometry of the metal-oxide system [15]. Therefore Oxygen vacancies are a good source for increasing the conductivities in n-type materials. Similarly for p-type materials, the conductivity is associated with metal interstitials. Although this picture is actually more complex, and the debate is still going on the actual reasons.

Therefore using this special property of AOS with metal cations, the thesis aims to optimize thin film transistor parameters and develop two major types of TFTs for driving and switching OLEDs:

- 1. Segmented Device: Single large size TFT to drive an 55mm<sup>2</sup> OLED

- 2. Pixelated Device: Single micron sized TFT to drive a pixel sized OLED.

The fabrication methodology for both the devices will be different and also the materials used, as the output parameters are different for both the devices. The optimization of the parameters includes ON-OFF Ratio, Sub-Threshold Swing, ON current, OFF Current, Gate Leakage and Mobility. The thesis is aimed to optimize these parameters and finally come up with an optimized process technology for a TFT that can drive and switch respective OLEDs and are compatible with industrial manufacturing standards.

## **Chapter 2: Literature Survey**

The patent for the first Field Effect Transistor was filed in 1926 and then in 1934 by Julius Edgar Lilienfeld and by Oskar Heil respectively [16, 17]. The first reports were actually concept patents demonstrating the novel idea of regulating the current flowing in a material using the effect of transverse electrical field. One of the first patented devices was a metal-semiconductor field-effect transistor MESFET, followed by the metal-insulator-semiconductor field-effect transistor MISFET.

The first practical demonstration of the field effect theory based device and the transistor effect was shown by Shockley and his team at Bell Labs in 1947, after the 20 year old patent by Lilienfeld eventually expired. The first practical semiconductor devices making use of this principle was JFET, and MOSFET, which is the bases of the semiconductor revolution was invented later in 1960 by Dawon Kahng and Martin Atalla.

Figure 3: Patent structures by Lilienfeld- MESFET (left) and MISFET (right)

The first working Thin Film Transistor was made by Paul K. Weimer at the RCA Laboratories in 1962. His findings were published in the paper, "The TFT — A New Thin-Film Transistor" in 1962 at the Proceedings of the IEEE, which attracted the attention of the scientists worldwide[18]. Weimer's demonstration was based on an insulated gate structure for a field effect transistor by printing layers of each component: CdS:CdSe (Cadmium Selenide) ink was used to print semiconductor;

Silicate cements was used as dielectric and Hg:In paste was used as conducting electrodes for source and drain.

Figure 4: Cross section and also the plan view of an evaporated thin film transistor [18, 19]

Figure 5: 1 inch square glass slide (attached on a lucite slab)with 3 TFT's fabricated on it [18, 19]

Figure 6: Characteristic curves for an experimental Cadmium Sulfide TFT designed for operation in the "enrichment" mode (Enhancement Mode) [18, 19]

The usage of oxide semiconductors for channel layers in TFTs existed earlier but the performance was not up to the mark. And it was only after 2003 that new and better device performances were reported [20, 21]. These devices with better electrical

characteristics were using ZnO as the semiconductor material for the TFTs and were made by Hoffman et al, Carcia et al. and Masuda et al [22-25]. Hoffman's TFTs were made using Transparent Conducting Oxide (TCO) for the electrodes hence fully optical (as ZnO is also transparent) with optical transmission of 75%, ON/off ratio of 10<sup>7</sup> and average mobility of 2.5 cm<sup>2</sup>V<sup>-1</sup> s<sup>-1</sup>. Carcia reported TFT fabrication at room temperature by using RF magnetron sputtering giving ON/OFF current ratio of 10<sup>6</sup> and mobility of 2 cm<sup>2</sup>V<sup>-1</sup> s<sup>-1</sup>. The interesting part is that both the experiments conducted by Hoffman and Carcia gave similar results with mobility better than TFT made using a-Si:H (amorphous Silicon) as semiconductor and more than organic TFTs as well. Results obtained by Masuda were a bit different with average mobility less than 1, ON/OFF ratio of 10<sup>5</sup> and optical transparency of 80%. However, in all the three devices the processing temperature required to anneal the semiconductor was as high as 723 - 873 K in order to get a good performance out of the device. After the demonstration of these results a lot of groups around the world started working on conductive oxides.

Thin Film transistor made using all-polymer technology with insulated gate structure using ink-jet printing was demonstrated for the first time by Sihvonen et al in 2000, inspired by Weimer's TFT [26]. Although the results of the printed TFT were not great, the work is considered as a big leap in printed electronics.

Initially ZnO was used extensively for the TFT fabrication as is it inexpensive and abundant. However, it was suggested that the use of complex materials like GIZO (InGaO<sub>3</sub>(ZnO)<sub>5</sub>) may give better results. The experiment for such device was successfully demonstrated by Nomura et al in 2003 with high mobility of 80 cm<sup>2</sup>V<sup>-1</sup> s<sup>-1</sup> and ON/OFF ratio of 10<sup>6</sup> [21]. The drawback of this device was that the annealing temperature required to obtain a single crystalline semiconductor layer epitaxially grown on an yttria-stabilized zirconia substrate for GIZO was 1673 K. Thereafter, Nomura et al also made use of flexible substrate to fabricate TFT upon it. This was done by depositing amorphous GIZO as semiconductor by Pulsed laser deposition (PLD) method. This device showed 9 cm<sup>2</sup>V<sup>-1</sup> s<sup>-1</sup> mobility and ON/OFF ratio of 10<sup>3</sup> mainly because of amorphous nature of the semiconductor leading to non-uniform structure [11]. It was a big step in achieving better mobility when fabrication is done at room temperature; hence since then a lot of studies have been done. Using

precursor solution for making semiconductor films by spin coating was also done by Ohva et al. but the processing temperature was much high of about 1173 K, and obtaining a mobility of 0.2 cm<sup>2</sup>V<sup>-1</sup> s<sup>-1</sup> and ON/OFF ratio of 10<sup>7</sup> [27]. More studies helped reducing the processing temperature and the deposition method was also changed. In 2011, Making use of the spray pyrolysis technique a mobility of 85 cm<sup>2</sup>V<sup>-1</sup> s<sup>-1</sup> was achieved with process temperature of 673 K by using Zinc and Lithium acetates for making the precursor solution (Li doped ZnO). This work was done by Adamapoulos et al. and they made us of the bottom gate configuration along with high-k dielectric (ZrO<sub>2</sub>) [28]. Adding Tin and Indium to dope ZnO was also used to improve the mobility and reduce the temperature. So IZO and ZTO were used in 2007 to obtain a mobility of 16 cm<sup>2</sup>V<sup>-1</sup> s<sup>-1</sup> with SiO<sub>2</sub> as dielectric and bottom gate configuration by Chang et al [29-31]. Lower temperature trials were done using GIZO as semiconductor by Yang et al. and Nayak et al. with mobilities of about 8  $cm^2V^{-1}$  s<sup>-1</sup> and processing temperature of about 473 – 723 K [32-35]. These experiments made use of the hydrothermal and sol get methods to deposit think films of semiconductor materials.

The temperature is a problem because the applications of the TFTs have a huge range and a lot of applications need flexible transparent substrate, all of which have low melting point. Therefore if the processing temperature in high, then it is not possible to print or deposit films on those substrates. To solve this problem, a new approach was tested by Banger et al which involved the use of organic – inorganic metal alkoxide precursor solution to get a layer of amorphous ternary and quaternary oxide semiconductor. This solution processed device gave performance equivalent to device made by sputtering the films, in terms of mobility (10 cm<sup>2</sup>V<sup>-1</sup> s<sup>-1</sup>) and threshold voltage stability, while keeping the temperature at about 503 K. This process is called sol-gel process and makes use of metal alkoxide precursor solution, with processing capability at lower temperatures [36].

In 2011, a new recipe methodology was used that involved self-energy generation combustion chemistry, which generated localized heat as the chemical reaction being exothermic. This helped to reduce the external requirement for heat to process the fabrication process. M G Kim et al used IO, ZTO and IZO to fabricate TFT with a processing temperature of 473 K [14]. Acetyl acetone or urea was used as fuels and

nitrates as oxidizers to deposit IO by self-combustion method. The TFT obtained in this process had a mobility of 6 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>. The bottleneck today still remains the processing temperature for the TFT devices. For the dielectric part, it determines the electric field present in the channel and the accumulation of the charges there. The leakage is also determined by the dielectric and cross linking in the dielectric is important to reduce the leakage. Popular dielectrics include Alumina and PVP-PMMA with added cross linking agents.

The surface of the substrate is important as well for the performance of the TFT device. Higher crystalline and smooth surface will scatter less electrons and hence will give better output results.

Figure 7: Timeline for Thin Film Transistors along with landmarks in IC development [37]

Table 1: Applications of TFTs [37]

| TFT Area        | Function             | Principles of Operation                                                                       |  |

|-----------------|----------------------|-----------------------------------------------------------------------------------------------|--|

| Gate Dielectric | pH Sensing           | H <sup>+</sup> adsorption in suspended gate<br>dielectric structure                           |  |

|                 | Memory               | PZT gate dielectric                                                                           |  |

| Semiconductor   | Gas Sensing          | H <sub>2</sub> O <sub>2</sub> alcohols, N <sub>2</sub> O adsorption on<br>semiconductor layer |  |

|                 | IR Detection         | $I_d = f(temperature)$                                                                        |  |

|                 | Gas Sensing          | H <sub>2</sub> decomposition on Pd gate electrode                                             |  |

| Gate Electrode  | Bio Sensing          | Biomolecule reaction with agents on gate electrode                                            |  |

|                 | Protein/DNA Analysis | Contact resistance change due to biomolecule adsorption                                       |  |

| S/D Electrodes  | Artificial Retina    | Photoconductivity change on attached<br>a-Si:H layer                                          |  |

|                 | X-ray imaging        | Scintillator light emission on attached diode                                                 |  |

|                 | LEDs                 | Quantum dot light emission                                                                    |  |

| Structures      | Photo sensing        | I <sub>light</sub> /I <sub>dark</sub> ratio enhanced by split or<br>offset gate               |  |

| Structures      | Memory               | Floating-gate dielectric                                                                      |  |

|                 | Magnetic             | Hall effects due to additional electrodes                                                     |  |

In this project the TFT fabrication is done in two stages, first one involves TFT fabrication for driving and switching fabricated segmented display and the second involves TFT fabrication for pixelated display. The parameters for the TFT were specified by the industrial collaborators at the beginning of the project and the aim of the project was to fabricate a TFT device to meet those parameters specified by the industry. To reach the desired parameters, various combinations and trials for each later of the TFT were done. Experiments were performed to improvise the substrate, semiconductor, dielectric, source-drain and gate electrodes. Since the final device was to be fabricated on a transparent substrate, Quartz was used for the purpose. The

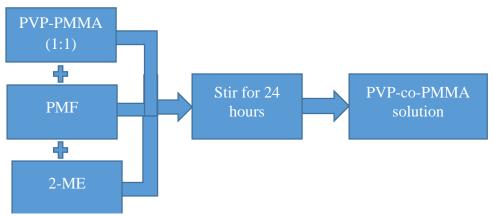

semiconductor used was Zinc Tin Oxide (ZTO) and experiments were carried out with the Zinc: Tin ratio, recipe methodology and the molarity of the solution. The dielectric used was Poly(4-vinylphenol-co-methyl methacrylate) i.e. PVP-co-PMMA and experiments were carried out with various recipes and additives in PVP-co-PMMA to make it a better dielectric and reduce the leakage. Finally experiments were performed with the source, drain and gate electrodes, to get a smooth surface and to achieve a good ohmic contact with the semiconductor.

## Chapter 3: Field Effect Transistor Theory

A Thin Film Transistor works on the principle of field effect theory. It is structured in layers or films of different materials, each of which exhibit their individual properties to combine and work as a transistor. The working principle of a TFT is similar to that of a MOSFET. Lilienfeld mentioned in his first patent about a metal semiconductor field-effect transistor (MESFET). The insulated gate FET (TFT) came later when proposed by Weimer in 1961. The layers in this device were formed through thermal evaporation using shadow mask technique to pattern each layer. For the semiconductor layer cadmium sulphide was used. A TFT is an Insulated-Gate FET with the same basic working principle of a MOSFET but with some structural differences [18].

A MOSFET is a four terminal device: The Silicon substrate body (B), the Source (S), the Drain (D) and the Gate (G). The contact source and drain are the input and the output terminals and the gate and the body contacts are used to apply bias voltage. Hence the output current flows between the source and the drain, and the gate is used to control this current flow, then the gate voltage is the basis of turning the transistor in ON state or in OFF state.

Figure 8: Schematic diagram of an n-cannel enhancement mode MOSFET [38]

The type of the charge carriers that assist in the source-drain current are used to classify the MOSFET. In an n-channel MOSFET the channel formation will be that of electrons while in case of a p-channel MOSFET it will be holes.

MOSFET can be classified on two other types as well based on their operation theory. These types are: Enhancement type and Depletion type MOSFET. Enhancement type is based on the channel formation only on the application of the gate voltage and hence is in OFF state when no voltage is applied, while in case of the depletion type MOSFET, the channel is already in formation and gate voltage is applied in order to turn the MOSFET to OFF state.

## 3.1 The Metal-Oxide-Semiconductor (MOS) Capacitor and Operation

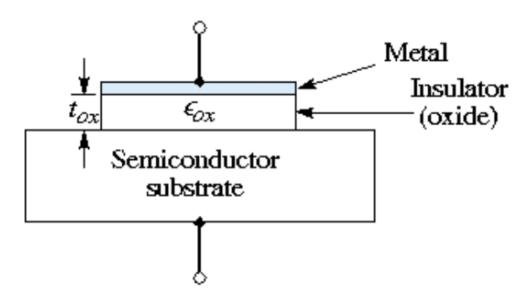

Figure 9: Basic MOS structure

An oxide layer is grown on top of a p/n-type semiconductor and a metal is placed on the oxide. The oxide layer provides isolation between the metal and the semiconductor. This was the structure of the MOS structure, which has changed a lot at present.

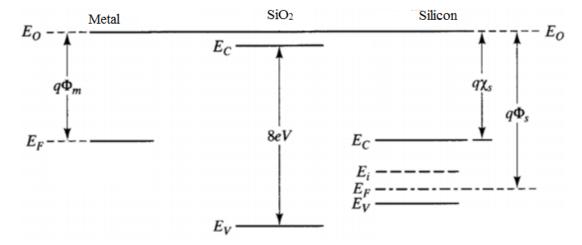

Figure 10: MOS band diagram before contact

In Fig. 10 we can see that the work function of the metal is less than that of the semiconductor. Hence, after the contact is made there will be charge transportation between the metal and the Silicon to as that the Fermi level of both gets aligned. This process will result in collection of electrons either at the metal interface or at the silicon interface depending on the work function of both. In the above specific case, as the work function of the metal is less, so the electrons will travel from the metal to the Silicon and a negative charge will collect at Si-SiO<sub>2</sub> interface.

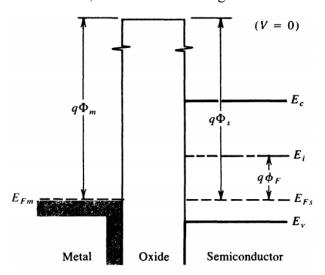

An ideal MOS capacitor band diagram will look like Fig. 11, but since there is a difference in the work function, the actual band diagram will look like Fig. 12.

Figure 11: Energy Band Diagram for an ideal Metal Oxide Semiconductor structure at equilibrium [39]

Figure 12: Band Diagram for MOS structure after contact

The Fig. 12 gives a band diagram in depletion mode, as there is a collection of electrons in the p-type semiconductor. The other cases are discussed further.

There are three cases possible:

- Accumulation Case

- Depletion Case

- Inversion Case

The Fermi levels of the metal and the semiconductors align themselves and there is no gradient. A potential barrier is formed between the metal and the semiconductor after the Fermi levels align. Due to difference in work function of the metal and the semiconductor, band bending occurs in the semiconductor.

Considering a specific case when the work function of the metal is less than the work function of the semiconductor and the semiconductor is of p-type we will obtain a depletion case. This happens because the work function of the metal is smaller than that of the silicon; electrons are transferred through the terminals of the device from the metal to the semiconductor. On the metal interface with the oxide, a thin sheet of surface positive charge is formed. On the semiconductor side, a voltage drop and an electric field are formed so that holes are driven away from the silicon adjacent to the surface of the oxide, leaving an excess of negatively charged ions. Therefore, the energy band in the semiconductor surface bends downwards.

The voltage drop across the insulator is a consequence of the charges stored on either side. Therefore a voltage needs to be applied to prevent this band bending. The Flat

Band Voltage is defined as the gate voltage applied to eliminate band bending at the surface of semiconductor and resulting in zero space charge in the region.

$$V_{FB} = \emptyset_M - \emptyset_S$$

$\emptyset_S$ : Work function of semiconductor and  $\emptyset_M$ : work function of metal If a bias voltage is applied further (after the application of  $V_{FB}$ ), then following effects take place:

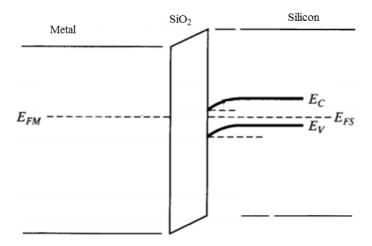

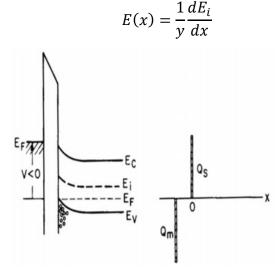

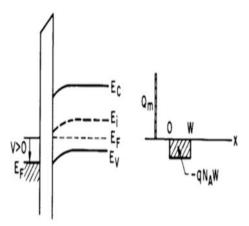

#### 3.1.1 Accumulation Case

When there is an application of negative voltage on the metal contact side, the energy bands near the semiconductor surface are bent upward. The Fermi level in the semiconductor remains constant. As there is negative voltage applied, the electrostatic potential of the metal id reduced as compared to that of the semiconductor. This increases the energies of the electrons on the metal terminal compared to semiconductor. Therefore,  $E_{FM}$  the metal Fermi level changes and is then increased to a position qV above its equilibrium state, when a voltage V is applied. The metal acquires a negative charge on the surface with the oxide interface. Holes accumulate near the oxide semiconductor interface. Hence in case of p-type substrates, we have a p+ type region at oxide-semiconductor interface.

This change in the metal Fermi energy level relative to EFS, changes the oxide conduction band and introduces a tilt in it. This tile in the oxide is caused by the gradient due to the electric field.

Figure 13: Accumulation Case in p-type

#### 3.1.2 Depletion Case

The application of positive voltage increases the electrostatic potential of the metal thereby decreasing the Fermi level of the metal by the factor qV compared to its equilibrium position. Similar tilt of oxide energy band is observed as in accumulation case but the electric field direction is opposite this time. Bending of the semiconductor bands also takes place, and this time in the downward direction as there are electrons accumulating near oxide-semiconductor interface. So electrons are removed and the metal gets positively charged on the application of positive voltage. This positive charge attracts electrons on the semiconductor side. Due to the electron attraction, the holes in the p-type get depleted in the region near the surface, with ionized acceptors left behind. This case can be compared with a p-n junction system.

The hole concentration reduces in the depleted region, therefore  $E_i$  shifts nearer to  $E_F$ , and band bending occurs in downward direction near the semiconductor surface.

Figure 14: Depletion Case in p-type

#### 3.1.3 Inversion Case

The effect seen in the depletion case will increase with the increase in the positive voltage applied. The bands will continue to bend more strongly, and at a sufficiently high voltage, the Fermi level will cross the  $E_i$ . In this case therefore,  $E_F >> E_i$  means that there is a large concentration of negative charge near the conduction band and hence and n-type thin layer is formed because of the inversion phenomenon in a p-type material, since:

$$n_0 = n_i e^{(E_F - E_i)/kT}$$

Figure 15: Inversion Case in p-type

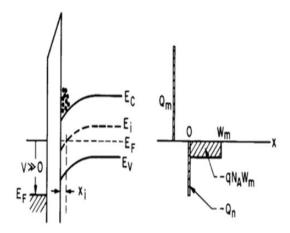

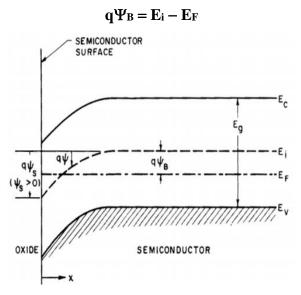

The MOSFET operated according to the inversion case, where the band bending to so much that the bulk potential and the interface/surface potential are much different.

The potential  $\psi$  is zero in the bulk semiconductor and  $\psi_s$  is the potential at the semiconductor surface, where  $\psi_B$  is Fermi potential.

Figure 16: Analytical relation for surface and bulk potentials

$$\Psi_s(inv) \approx 2\Psi_B = \frac{2kT}{q} \ln \left[ \frac{N_A}{n_i} \right]$$

kT/q= Thermal Voltage=  $V_T$  = 26 mV at room temperature (T= 300K)

N<sub>A</sub>= Concentration of acceptor atoms

$n_i$ = Intrinsic Carrier concentration =  $10^{10}$  cm<sup>-3</sup> in silicon at room temp (T= 300K)

Hence we finally have (for p-type):

| $\psi_{\rm s}$ < 0      | Hole Accumulation (bands bend upward)       |  |  |  |

|-------------------------|---------------------------------------------|--|--|--|

| $\psi_s = 0$            | Flat-band condition                         |  |  |  |

| $\psi_B > \psi_s > 0$   | Hole Depletion (bands bend downward)        |  |  |  |

| $\psi_s=\psi_B$         | $n_S = n_P = n_i$ (intrinsic concentration) |  |  |  |

| $W_{\rm s} > W_{\rm B}$ | Inversion (bands bend downward)             |  |  |  |

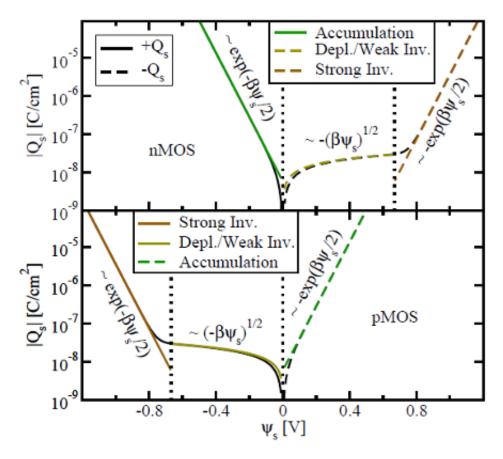

Figure 17: The surface charge density  $Q_S$  compared for both p-type and n-type semiconductors depending on.  $\psi_{S}$ . While the solid lines stand for positive  $Q_S$ , the dashed lines symbolize negative  $Q_S$ . [40]

# 3.2 MOSFET Operation

A MOSFET is a voltage controlled switch, as the application of the gate voltage controls the current flow between the source and the drain. Consider a p-type substrate and two n-wells formed in it, hence making an n-channel MOSFET or NMOS.

The well formation takes place mainly by ion implantation method. For n-well electron rich impurities like Phosphorus and Arsenic are added. The gate dielectric is a high-k dielectric to isolate the gate contact and the channel and also to provide maximum electric field to create a channel. Currently dielectrics like hafnium silicate, zirconium silicate, hafnium dioxide and zirconium dioxide are used to provide good capacitance with lesser area coverage. At the boundary of a single MOSFET we have field oxide that is used to isolate and provide reducing in electrical interference.

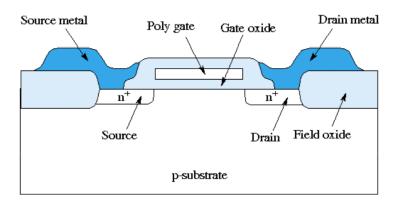

Figure 18: Cross section view of an n-channel MOSFET, showing the field oxide and polysilicon gate [38]

When the voltage on the gate terminal is positive compared to the substrate (which is also grounded like the source contact, hence  $V_G$  or  $V_{GS}$ ), positive charges then start to deposit on the gate contact terminal. The electrostatic force of these positive charges on the gate terminal induces negative charges in the channel below and also repels away the holes present. These induced charges are actually the channel formed between the source and the drain terminal. This charge introduction in the form of a channel is because of the inversion case, where the Fermi level at the interface crosses the intrinsic level hence we have the inversion condition:

$$\Psi_{\rm s}(inv) \approx 2\Psi_{\rm R}$$

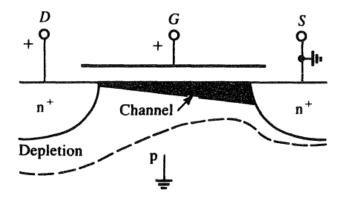

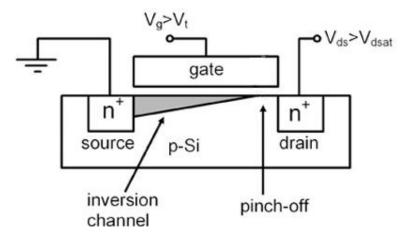

Figure 19: Channel formation in an NMOS with the application of gate voltage and drain voltage [39]

The function of the gate voltage is to induce the channel formation, but without the application of the drain voltage ( $V_D$  or  $V_{DS}$ , since source terminal is grounded) no current will flow between source and drain. Hence for a particular  $V_G$  the drain current ( $I_D$ ) will increase with increase in the  $V_D$ , and the will saturate after a particular voltage. Therefore the function of the gate voltage is as a switch to allow the current to pass from source to drain.

## 3.3 MOSFET Characteristics

# 3.3.1 Output Characteristics

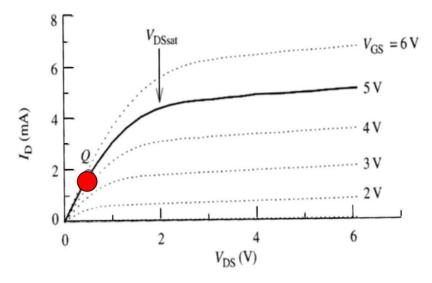

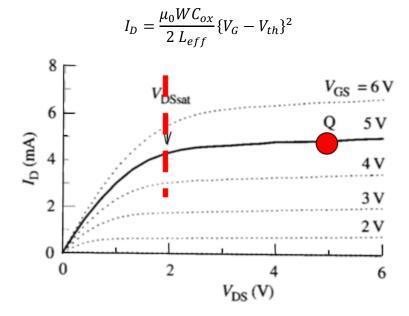

The plot between the drain current and the drain voltage with variable step values for gate voltage are called output characteristics. The linear region in the plot that starts from the origin is called the triode region and it is during the formation of this region that the current level at the drain terminal is increased. After a particular drain voltage the drain current saturates, and this point is called Pinch-off Voltage ( $V_{DSat}$ ). Hence for the linear/ triode region we have:

$$V_G > V_{th}$$

and  $0 < V_D < V_{DSat}$

$$I_{D} = \frac{\mu_{0}WC_{ox}}{L_{eff}} \left\{ (V_{G} - V_{th})V_{DS} - \frac{V_{DS}^{2}}{2} \right\}$$

Where, $\mu_0$ : Mobility,

W: Channel width

Cox: Oxide (dielectric) capacitance

L<sub>eff</sub>: Effective channel length

Figure 20: NMOS output characteristics for linear/triode region

After the voltage is increased further than  $V_{DSat}$ , the transistor goes into saturation region, where the effect of drain voltage on drain current is negligible and hence the current saturates. This is the ON regions of the transistor. Now at the pinch off point, the inversion region in the channel starts retracting away from the drain terminal because of the high drain voltage, now the vertical electric field that was holding the charges in the channel becomes horizontal and so the thickness of the channel at the drain terminal reduces greatly. Hence the channel now entered the saturation region.

$$V_G > V_{th} \ and \ V_D > V_{DSat}$$

Figure 21: NMOS output characteristics for saturation region

Figure 22: NMOS in saturation region showing Pinch-off region

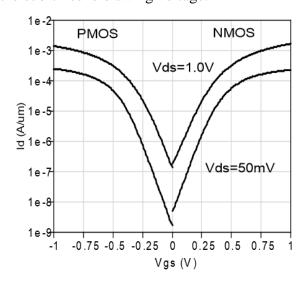

#### 3.3.2 Transfer Characteristics

For a MOS structure there is a particular gate voltage required to induce the formation of the channel. This minimum gate voltage is called the Threshold Voltage  $(V_{th})$ . Hence in order to have conduction, the gate voltage must be more positive than the threshold voltage for an NMOS and more negative than the threshold voltage for a PMOS. With the application of these voltages, the channel will be introduced and if there is a proper amount of drain voltage, the MOSFET will be said to be in ON state.

The transfer characteristics are the plot of drain current and the gate voltage at a particular drain voltage. These characteristics are most important to understand the device as we can extract a lot of parameters from the plot like mobility, on-off ratio, threshold voltage and sub-threshold swing voltage.

Figure 23: Transfer Characteristics of a 32 nm Intel PMOS and NMOS showing  $\sim 100 mV/decade$  slope at  $V_{DS}=1.0V$  and 50 mV [41]

Threshold Voltage (V<sub>th</sub>): It's if the most important parameter for a device, as

it defines the voltage at which surface potential is double that of the body

potential. The physical meaning of threshold voltage is that an electron

channel with large electron concentration is formed on the surface of the

semiconductor.

$$V_{GS}$$

< $V_{th}$ , cut off mode  $V_{GS}$ > $V_{th}$ , on-mode

A positive effective gate voltage repels the holes from the silicon surface, leaving behind uncompensated negative acceptor ions. The charge is called depletion-layer charge.

Density of the depletion charge: Qd = qNaW

The effective voltage drop across the dielectric capacitor is:

$$V_{GS} - V_{FB} - \psi_S = \frac{Q_d}{C_{ox}}$$

(For V<sub>GS</sub> < V<sub>th</sub>)

At the threshold,  $V_{GS}=V_{th}$  and  $\psi_S=2$   $\psi_B$ , therefore

$$V_{th} = V_{FB} + 2\psi_B + \frac{Q_d}{C_{ox}}$$

• Mobility: It is an important factor while designing a device. It is the parameter that helps in differentiating between the devices and their capabilities. Mobility for devices based on Silicon is very high as compared to metal oxide based devices. The mobility measurement for a field effect device can be divided in two regions, first mobility for the linear region of the output characteristics and the other is the mobility for the saturation region. These can be calculated as follows:

$$\mu_{lin} = \frac{L}{C_G W V_D} \left( \frac{\mathbf{\partial} I_{Dlin}}{\mathbf{\partial} V_G} \right)$$

and

$$\mu_{sat} = \frac{L}{C_G W} \left( \frac{\mathbf{\partial}^2 I_{Dsat}}{\mathbf{\partial} V_G^2} \right) = \frac{2L}{C_G W} \left( \frac{\mathbf{\partial} \sqrt{I_{Dsat}}}{\mathbf{\partial} V_G} \right)^2$$

Hence the mobility values can be found out using these equations. So when we have  $V_D < V_G$  -  $V_{th}$ , the mobility data will correspond to linear mobility

and when  $V_D \ge V_G - V_{th}$ , then the mobility will be saturation mobility. If we plot  $\sqrt{I_{Dsat}}$  with respect to  $V_G$ , we will get a straight line, in which the square of the slope will be proportional carrier mobility. If we extrapolate the linear part of the curve to intersect the Gate voltage axis, we will get the  $V_{th}$ .

• Subthreshold Swing (S): It is another important parameter that determines the performance of the field effect device. The value of subthreshold swig give the measure of how efficient is the channel formation with respect to the gate voltage. Hence it give the change in the drain current with respect to gate voltage. Higher the change in drain current for a given value of gate voltage the better the device is. It is the inverse of the slope of the transfer characteristic curve of the device and is measure in V/decade as its unit. The formula to determine subthreshold swing is:

$$S = \frac{\partial V_G}{\partial (log_{10}I_D)}$$

• ON/OFF Ratio: This is the last important measurement parameter for a device. The ON/OFF ratio as the name suggests, gives the ratio of the ON drain current and the OFF drain current. This is important because a higher ON/OFF ratio will ensure proper ON current while the device is switched ON and less leakage while the device is switched OFF. It is a unit less parameter and has a typical value of 10<sup>6</sup> for modern devices.

# 3.4 Comparison of a MOSFET and a Thin Film Transistor (TFT)

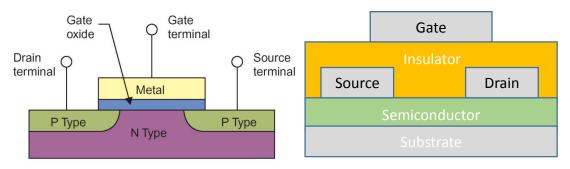

A TFT is also a Field Effect Transistor (FET) like MOSFET, but with some structural and operational differences. A TFT unlike a MOSFET is a layered planar structure.

Figure 24: MOSFET (left) and TFT (right)

While in a MOSFET the source and drain are made by ion implantation of the dopant inside the substrate, where as in case of the TFT, the source and drain are made of metal and are directly used for contact terminals. In case of a MOSFET, the channel is formed in the substrate itself, but in a TFT, the substrate is just a support to fabricate the device. MOSFET is typically of the same structure as in the figure with source and drain in the same plane and then above them will be a dielectric and then a metal gate, but in case of a TFT the structure can vary a lot. Following are the possible structures possible in case of a TFT:

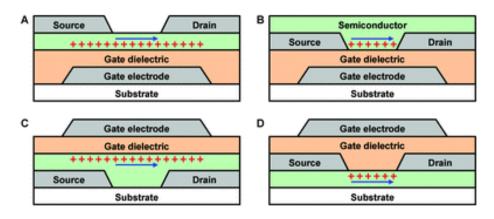

Figure 25: Different types of TFT structures [42]

- A: Bottom-gate (inverted) staggered TFT

- B: Bottom-gate (inverted) coplanar TFT

- C: Top-gate staggered TFT

- D: Top-gate coplanar TFT

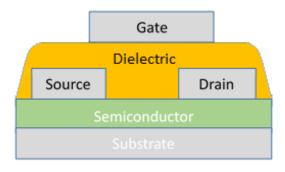

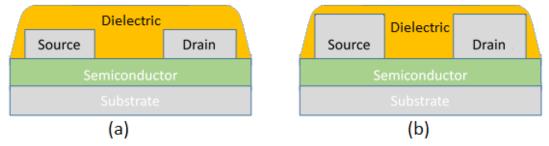

The structure selected for an application depends mainly on the factors related to the purpose of the application and limitations due the fabrication process of the TFT to be made. For example, the Bottom-gate (inverted) staggered TFT is widely used for the fabrication of a-Si:H TFT, because of easy fabrication process and better electrical properties [43]. However, in case of the experiments performed in this thesis, the structure used is a Top-gate coplanar TFT, due to the metal used as source and drain contact i.e. Aluminium, which has melting point (933.47 K) close to the annealing temperature for the semiconductor used (773 K), hence it may result in destruction of the source and drain contact by the oxidation of the Aluminium.

Another difference is the use of the device, while a MOSFET is used mainly in a computing application and applications where high speed and performance is needed, a TFT is used for low cost applications where main concern is ease of fabrication, substrate flexibility and transparency, and the speed is not a concern like in display applications.

The working of the TFT is also a bit different compared to a MOSFET. A MOSFET while works when there is an inversion region formed in the channel, a TFT works upon the formation of accumulation region. Therefore for an NMOS-enhancement type MOSFET, a positive voltage would be applied to create a channel of n-type in a p-type semiconductor, while in a TFT positive voltage will be applied to create n+type channel but in an already n type semiconductor. Although there are inversion case TFTs as well, but there are no accumulation case MOSFETs used.

# **Chapter 4: Experimental Procedure**

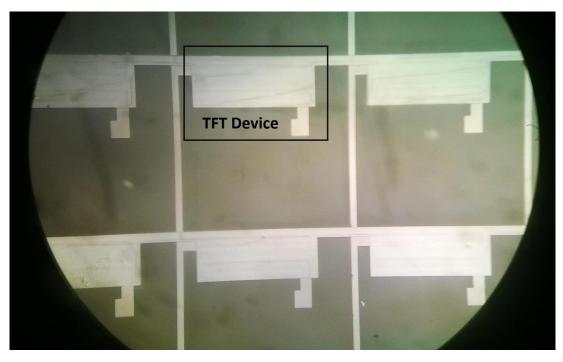

The experimental design is such that it is done for two different types of structures, namely segmented device and the pixelated device. As the name suggests the pixelated device is much smaller than the segmented device. The purpose of both is the same but the application areas are different. The segment TFT design will be used to drive and control the large area OLED displays, whereas the pixelated device will be used to control small OLED displays.

The improvisation and optimization of the device is carried out with each layer of the TFT structure. In general, the semiconductor used is Zinc Tin Oxide (ZTO) with variable concentrations, the dielectric used in Poly (4-vinylphenol-co-methyl methacrylate) i.e. PVP-co-PMMA with some additives of poly(melamine-co-formaldehyde) i.e. PMF. The device characterization system used was 4200 Keithley Semiconductor Characterization System. TTP4 Cryogenic Probe Station by Desert Cryogenics was used for nano probing the devices for characterization. For the lithography processes, Karl Suss MJB4 Mask Aligner was used to make the source, drain and gate contacts.

In order to fabricate the two types of devices segmented and pixelated, the process was almost the same except the use of lithography for the pixelated device. Now, the next section will include the details about the device fabrication and processes. There are some common initial processes that are same for both the segmented and the pixelated device, like substrate cleaning and precursor preparation. These processes will be discussed initially and then the fabrication process for each of the type of TFT will be discussed individually.

Figure 26: Final TFT device schematic

# 4.1 Substrate Preparation

The substrate preparation involves two steps: cleaning and activating the surface of the substrate (which in this case is Quartz). The cleaning of the substrate is very important. It involves a few processes to remove any dust or chemical adhering to the surface of the substrate. Hence, the process involves a mechanical procedure to remove dust and a chemical procedure to remove or dissolve any chemical impurity present.

The Quartz substrates were cleaned by submerging them in Acetone containment and sonicating the containment in ultrasonic bath for 15 minutes at room temperature. The purpose of the Acetone is to dissolve any chemical impurity and the ultrasonic treatment will rub away any dust particle attached on the substrate.

After this procedure, the samples were taken out and air gun (Nitrogen) was used to speed blow the acetone from the substrate. Thereafter the substrate is taken for UV-Ozonation.

The cleaning of the sample is done when the high energy UV light which is irradiated on the surface of the sample causing oxidation. This reaction is a photo sensitive oxidation which atomizes the Oxygen. So the UV is exposed on the heated substrate to start this reaction, making the surface hydrophilic and in return, volatile hydrocarbons come out as end product. UV-Ozonation is the process to activate the substrate surface by making it hydrophilic. This is done by exposing the heated surface of the substrate to UV radiations, which in air combine Oxygen atoms to form Ozone, which subsequently reacts chemical present on the surface to form water and get vaporized. Usually the temperature is set to be 150° C and the process is carried on for 20 minutes.

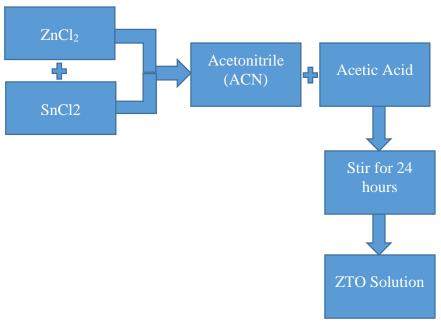

# **4.2** Semiconductor Precursor Synthesis (ZTO)

For both the pixelated and the segmented devices, the semiconductor used was Zinc Tin Oxide (ZTO) with variations in the molar ionic concentration and annealing temperature.

ZTO is a wide band gap n-type semiconductor material with the chemical formula:

$$(ZnO)_x(SnO_2)_{1-x}$$

, where  $0 < x < 1$